Máy mình toàn thấp nhất 64gb,mua d5 cũng không chịu được nhiệtcó game là 0%, có cái là 10%

You are using an out of date browser. It may not display this or other websites correctly.

You should upgrade or use an alternative browser.

You should upgrade or use an alternative browser.

tin tức AMD chính thức ra mắt thế hệ CPU Ryzen 7000

- Thread starter Trí thức yêu Nước

- Start date

Morgan le Fay

Senior Member

quan trọng là nó đắt hơn gấp đôi mà hiệu năng không hơn gấp đôi, mua khá là phí tiềnMáy mình toàn thấp nhất 64gb,mua d5 cũng không chịu được nhiệt

pokenguyen

Senior Member

Em mới ngồi check giá thì:quan trọng là nó đắt hơn gấp đôi mà hiệu năng không hơn gấp đôi, mua khá là phí tiền

GIGABYTE Z690: 183e

Card Wifi: 30e

13700K: 459e

DDR4 3600CL16: 110e

=> 782e

GIGABYTE B650 Wifi: 195e

7700X: 398e

DDR5 6000CL34: 185e

=> 778e

Sao cuối cùng AMD lại rẻ hơn thế này

Last edited:

KnightRiot

Senior Member

có 2 con trâu cày 89 91%mới để ý sign

6 con 980ProĐại gia mua về chạy RAID à

Morgan le Fay

Senior Member

13700k vốn dĩ cạnh tranh 7900x màEm mới ngồi check giá thì:

MSI Z690/B660 Tomahawk: 210e

13700K: 459e

DDR4 3600CL16: 110e

=> 779e

GIGABYTE B650: 195e

7700X: 398e

DDR5 6000CL34: 185e

=> 778e

Sao cuối cùng AMD lại rẻ hơn thế này

pokenguyen

Senior Member

13700k vốn dĩ cạnh tranh 7900x mà

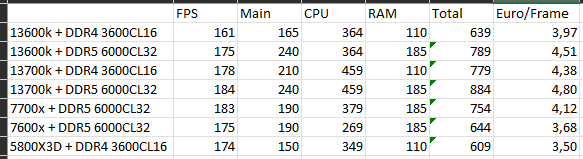

7900x em đú không nỗi bác ơi. Theo bảng này thì chắc em chọn 7700x hoặc 13600k. 13600k thì không cần main xịn.

GIGABYTE B660: 165e

13600K: 364e

DDR4 3600CL16: 110e

=> 639e

GIGABYTE B650 Wifi: 195e

7700X: 379e

DDR5 6000CL34: 185e

=> 759e

Dàn AMD mắc hơn 120e, vậy Intel ngon hơn hả bác?

Streamroller

Member

hy vọng AMD sẽ sớm triển khai RDNA3 trên APU, có phép triển khai MCD, IGP có IF cache và CPU coi IF cache như DDRAM cache (AMD có bằng sáng chế sử dụng DDRAM cache:https://www.freepatentsonline.com/y2022/0318151.html). Old man nghèo khổ có lẽ chỉ mong điều này.

Có tin đồn Zen 5, AMD sẽ tăng dung lượng L1 cache, bỏ L3 cache, thay vào đó L2 cache chia sẻ giữa các CCX. Chưa biết 1 CCX Zen 5 sẽ có bao core. TSMC 5nm có nhược điểm là mạch dành cho cache thu nhỏ cực thấp. 32MB cache trên 5nm chỉ nhỏ hơn 30% so với 7nm, do vậy die Zen 4 vẫn rất to. IF cache sẽ trở thành L3 cache chia sẻ giữa các CCX. Không gian AM5 vẫn khá đủ cho phép thêm 2 MCD, nhưng lại ko đủ để thêm 2 CCD. Muốn tăng thêm core trên AM5 là bất khả kháng nếu ko bỏ L3 cache trên CCD. MCD xếp chồng thêm 2 lớp sẽ mang đến 2x16x3= 96 MB, cũng ko phải là nhỏ.

Có tin đồn Zen 5, AMD sẽ tăng dung lượng L1 cache, bỏ L3 cache, thay vào đó L2 cache chia sẻ giữa các CCX. Chưa biết 1 CCX Zen 5 sẽ có bao core. TSMC 5nm có nhược điểm là mạch dành cho cache thu nhỏ cực thấp. 32MB cache trên 5nm chỉ nhỏ hơn 30% so với 7nm, do vậy die Zen 4 vẫn rất to. IF cache sẽ trở thành L3 cache chia sẻ giữa các CCX. Không gian AM5 vẫn khá đủ cho phép thêm 2 MCD, nhưng lại ko đủ để thêm 2 CCD. Muốn tăng thêm core trên AM5 là bất khả kháng nếu ko bỏ L3 cache trên CCD. MCD xếp chồng thêm 2 lớp sẽ mang đến 2x16x3= 96 MB, cũng ko phải là nhỏ.

Morgan le Fay

Senior Member

đúng rồi thím ơi, con này cạnh tranh với 7700x vẫn khá ngon7900x em đú không nỗi bác ơi. Theo bảng này thì chắc em chọn 7700x hoặc 13600k. 13600k thì không cần main xịn.

View attachment 1512174

GIGABYTE B660: 165e

13600K: 364e

DDR4 3600CL16: 110e

=> 639e

GIGABYTE B650 Wifi: 195e

7700X: 379e

DDR5 6000CL34: 185e

=> 759e

Dàn AMD mắc hơn 120e, vậy Intel ngon hơn hả bác?

pokenguyen

Senior Member

Theo bác thì 120e có đáng ko bác? Tại con 7700X sau này lên 7800X3D thì chỉ cần thay CPU còn con 13600K hết đường nâng cấp (lên 13900K thì VRM ko chịu nổi).đúng rồi thím ơi, con này cạnh tranh với 7700x vẫn khá ngon

Morgan le Fay

Senior Member

là em thì em mua 7600x rồi nâng lên x3D sau này, vì hiệu năng chơi game 7700x với 7600x không quá nhiều khác biệtTheo bác thì 120e có đáng ko bác? Tại con 7700X sau này lên 7800X3D thì chỉ cần thay CPU còn con 13600K hết đường nâng cấp (lên 13900K thì VRM ko chịu nổi).

sau đó sau này lên 7800x3D

hơn nữa main này lên được Zen 5 nên vẫn còn đường nâng cấp sau này

phanhaugiang

Member

Đề nghị không ban phát hi vọng cho các oldmanhy vọng AMD sẽ sớm triển khai RDNA3 trên APU, có phép triển khai MCD, IGP có IF cache và CPU coi IF cache như DDRAM cache (AMD có bằng sáng chế sử dụng DDRAM cache:https://www.freepatentsonline.com/y2022/0318151.html). Old man nghèo khổ có lẽ chỉ mong điều này.

Có tin đồn Zen 5, AMD sẽ tăng dung lượng L1 cache, bỏ L3 cache, thay vào đó L2 cache chia sẻ giữa các CCX. Chưa biết 1 CCX Zen 5 sẽ có bao core. TSMC 5nm có nhược điểm là mạch dành cho cache thu nhỏ cực thấp. 32MB cache trên 5nm chỉ nhỏ hơn 30% so với 7nm, do vậy die Zen 4 vẫn rất to. IF cache sẽ trở thành L3 cache chia sẻ giữa các CCX. Không gian AM5 vẫn khá đủ cho phép thêm 2 MCD, nhưng lại ko đủ để thêm 2 CCD. Muốn tăng thêm core trên AM5 là bất khả kháng nếu ko bỏ L3 cache trên CCD. MCD xếp chồng thêm 2 lớp sẽ mang đến 2x16x3= 96 MB, cũng ko phải là nhỏ.

pokenguyen

Senior Member

Nếu em xuống 7600X thì giá tổng bằng 13600K bác, chắc em đi đường này. Cảm ơn bác.là em thì em mua 7600x rồi nâng lên x3D sau này, vì hiệu năng chơi game 7700x với 7600x không quá nhiều khác biệt

sau đó sau này lên 7800x3D

hơn nữa main này lên được Zen 5 nên vẫn còn đường nâng cấp sau này

Ủa em không hiểu vụ nâng cấp lắm. Nếu em mua 7600X 270e, 7700x 380e, năm sau em bán thì 7600x 110e, 7700x 200e, cả 2 đều lỗ như nhau mà bác.

pokenguyen

Senior Member

Dùng kết quả ở

rồi cập nhật giá ở Đức thì ra vầy.

Chắc lấy combo 7600x quá

Chắc lấy combo 7600x quá

pokenguyen

Senior Member

5800X đang xài bị nghẽn mà bácnhầm

5800x ngon rồi đó

Xài màn 1440p bác, kiểu này chắc không lên 4k nỗi.5800x3d với 3080 là combo bao đẹp đó mai fen

Mà fen chơi game ở res nào đã?

BBearQ

Senior Member

Hóng đám Phoenix trên lap, code thì R× 7×40. Đám 7×45 là Dragon Range với việc max 16C/32T thì chắc chắn là igpu chống mù như desk để tận dụng discrete.hy vọng AMD sẽ sớm triển khai RDNA3 trên APU, có phép triển khai MCD, IGP có IF cache và CPU coi IF cache như DDRAM cache (AMD có bằng sáng chế sử dụng DDRAM cache:https://www.freepatentsonline.com/y2022/0318151.html). Old man nghèo khổ có lẽ chỉ mong điều này.

Có tin đồn Zen 5, AMD sẽ tăng dung lượng L1 cache, bỏ L3 cache, thay vào đó L2 cache chia sẻ giữa các CCX. Chưa biết 1 CCX Zen 5 sẽ có bao core. TSMC 5nm có nhược điểm là mạch dành cho cache thu nhỏ cực thấp. 32MB cache trên 5nm chỉ nhỏ hơn 30% so với 7nm, do vậy die Zen 4 vẫn rất to. IF cache sẽ trở thành L3 cache chia sẻ giữa các CCX. Không gian AM5 vẫn khá đủ cho phép thêm 2 MCD, nhưng lại ko đủ để thêm 2 CCD. Muốn tăng thêm core trên AM5 là bất khả kháng nếu ko bỏ L3 cache trên CCD. MCD xếp chồng thêm 2 lớp sẽ mang đến 2x16x3= 96 MB, cũng ko phải là nhỏ.

BBearQ

Senior Member

Bình tĩnh đợi 7kx3d để giá main ram cùng ổn định rồi tính tiếp nha

pokenguyen

Senior Member

Phải đổi case trước 9/12 bác ơi, sắp ra mùa POE mới rồi. Con case hiện tại ko chơi nỗi 3080.Bình tĩnh đợi 7kx3d để giá main ram cùng ổn định rồi tính tiếp nha

thaigiang

Đã tốn tiền

thay GPU là hết ngẽn nhéChơi game với 2070 thôi mà con CPU nó nghẽn như vầy thì nên up 5800X lên 7600X hay 7700X bác. Trong task manager thấy CPU chỉ 60% thôi.

Mua màn 144hz mà chơi chưa được 60hz.

View attachment 1512014

pokenguyen

Senior Member

thaigiang

Đã tốn tiền

ông ko tin tôi sao ? gaming gì tôi test choCPU bị nghẽn mà bác.

View attachment 1512362

Similar threads

- Replies

- 172

- Views

- 13K

- Replies

- 35

- Views

- 3K

- Locked

- Replies

- 170

- Views

- 11K

- Replies

- 0

- Views

- 94