Mr.Y

Team vòi xịt

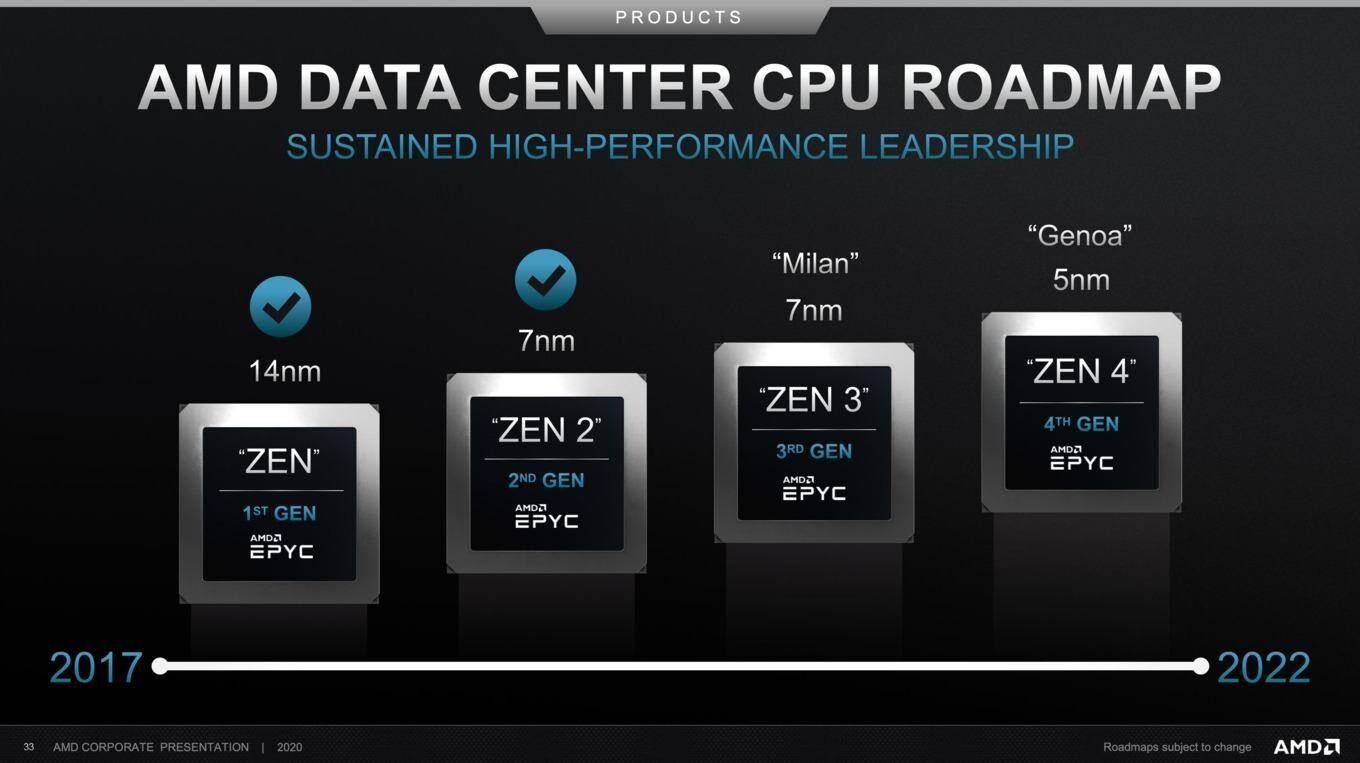

Theo một báo cáo được sự cho phép của Hardwareluxx, cộng tác viên Andreas Schiling đã có quyền truy cập vào tài liệu OEM. Theo Andreas, các bộ xử lý EPYC Milan sắp tới của AMD sẽ cải tiến hiệu suất lên đến 20% so với thế hệ EPYC trước đó. Báo cáo tuyên bố hiệu suất IPC là 15%, kết hợp thêm 5% được bổ sung thông qua tối ưu hóa xung nhịp hoạt động. Báo cáo tuyên bố rằng các thiết kế 64 lõi của AMD sẽ có xung nhịp đa lõi thấp hơn.

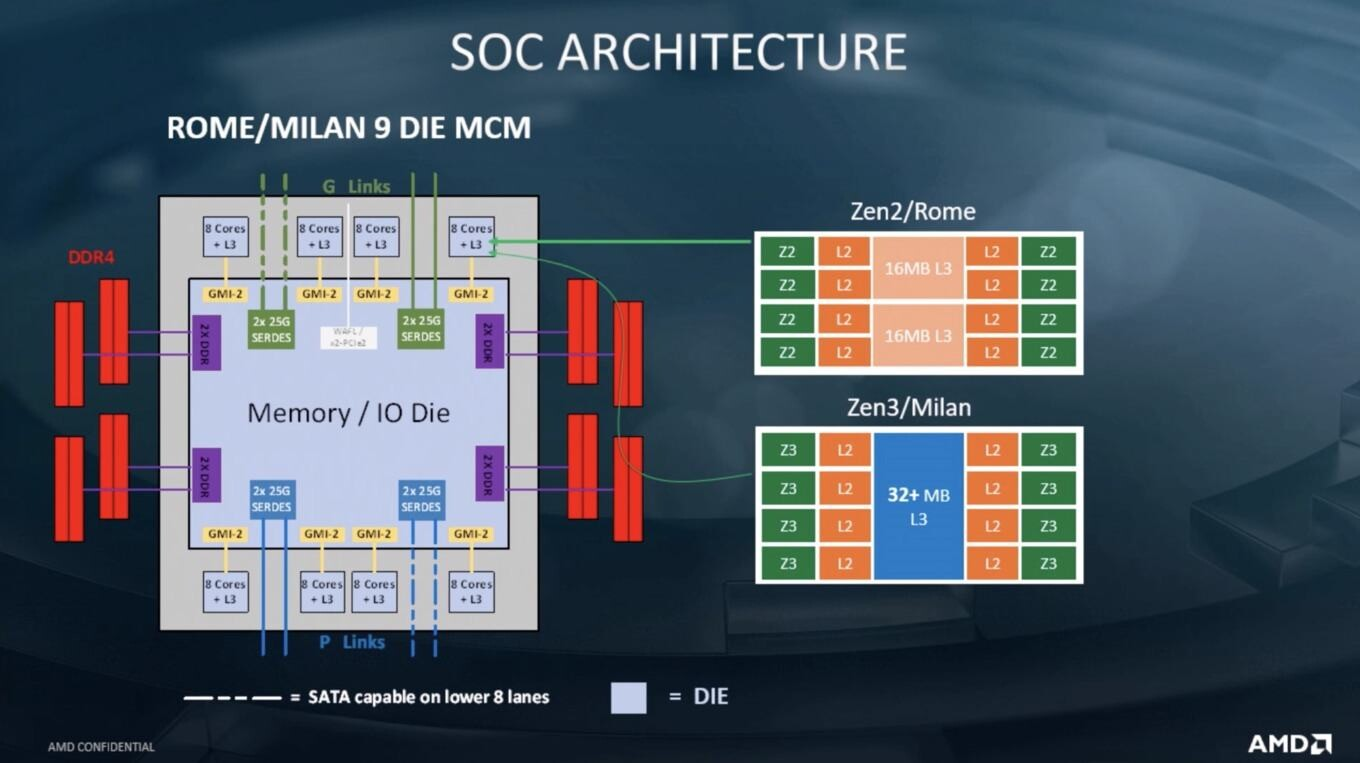

Rõ ràng, cách tiếp cận của AMD đối với kiến trúc Zen 3 loại bỏ các phân khu L3 theo CCX, giờ đây bộ nhớ đệm L3 đầy đủ 32MB có sẵn cho mỗi Core Compute Die (CCD) 8 lõi. AMD đã đạt được mức độ tối ưu hóa xung nhịp mới trên Zen 3, với giới hạn xung nhịp tăng cao hơn trước.

Điều này sẽ làm tăng công suất của các thiết kế có số lượng lõi thấp hơn vì nhiệt lượng tỏa ra ít hơn so với các thiết kế có nhiều lõi hơn. Milan vẫn giữ nguyên công nghệ sản xuất dựa trên quy trình 7nm, DDR4, PCIe 4.0 và TDP từ 120-225W như Rome thế hệ trước.

Theo techpowerup

Rõ ràng, cách tiếp cận của AMD đối với kiến trúc Zen 3 loại bỏ các phân khu L3 theo CCX, giờ đây bộ nhớ đệm L3 đầy đủ 32MB có sẵn cho mỗi Core Compute Die (CCD) 8 lõi. AMD đã đạt được mức độ tối ưu hóa xung nhịp mới trên Zen 3, với giới hạn xung nhịp tăng cao hơn trước.

Điều này sẽ làm tăng công suất của các thiết kế có số lượng lõi thấp hơn vì nhiệt lượng tỏa ra ít hơn so với các thiết kế có nhiều lõi hơn. Milan vẫn giữ nguyên công nghệ sản xuất dựa trên quy trình 7nm, DDR4, PCIe 4.0 và TDP từ 120-225W như Rome thế hệ trước.

Theo techpowerup